#시작하기 전에

이 기사는 '[강해령의 하이엔드 테크] 3D 낸드 특집: 잘 봐, 언니들 '쌓기' 싸움이다!<1>' 에서 이어지는 기사입니다. 1탄 에서는 3D 낸드 구성과 동작 원리에 대해 설명했습니다. 먼저 보고 오신다면 흐름이 훨씬 이해하기 쉬우실 거예요. 1탄 링크는 ‘이 곳’을 클릭해주세요. 아래 준비한 2탄은 ‘미래 낸드 공정’ 위주로 다뤘습니다. *링크로 넘어가지 않는다면 아래 댓글에 주소를 남겨뒀으니 참고해주세요.

◇낸드플래시 공정, 어떻게 진화할까

이제 3D 낸드플래시 제조 공정을 간략히 살펴보려고 합니다. 또 아래 미래 기술을 전망하는 부분은 최근 'IEDM 2021' 행사에 기조 연설자로 나섰던 김기남 삼성전자 종합기술원 회장의 낸드 기술 전망 발표 자료를 참고했습니다.

3D 낸드 제조 공정은 대략 이렇게 흘러갑니다.

① 맨 먼저 정보 저장 외 부수적인 작업을 맡는 주변회로부(Periphery) 제조 공정이 이뤄집니다.

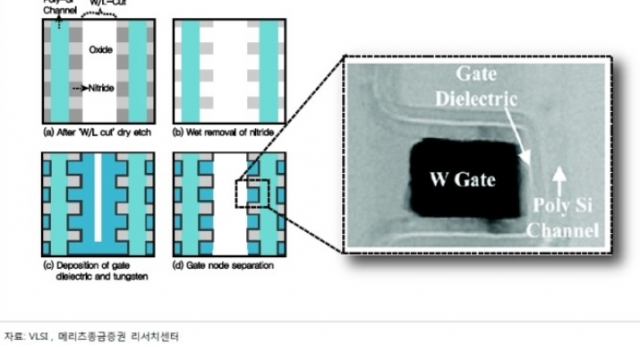

② 그 다음 셀 기초 공사를 합니다. 질화막(a.k.a 나이트라이드) 층, 셀 사이 칸막이 역할을 하는 산화막 층이 한 세트가 돼 100단 이상 쌓습니다.

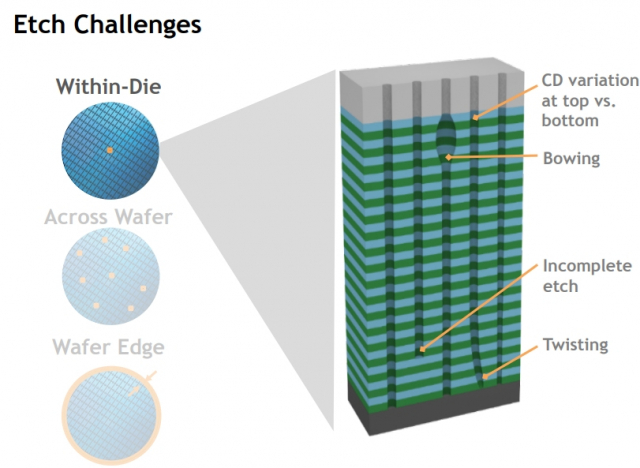

③ 여기에 수억 개 채널 홀을 뚫습니다. 한번에 깊고 정교하게 뚫을 수록 좋습니다. 또 채널홀에 채널, 트랩층, 산화막(옥사이드) 층을 차근차근 채웁니다.

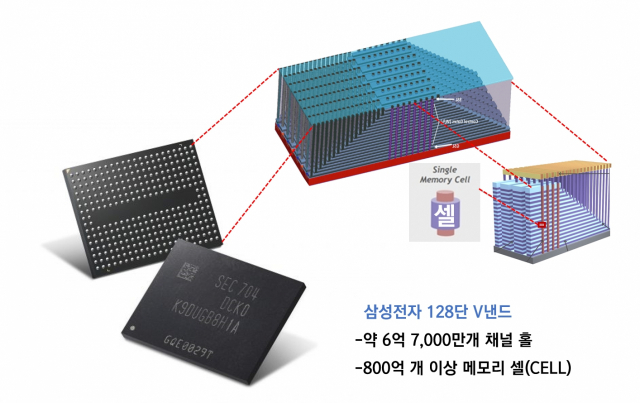

④ 채널홀 공정이 끝나면 홀 옆에 도랑을 팝니다. 질화막을 걷어내기 위해서인데요(왼쪽 그림의 (b)). 걷어낸 자리에는 전기가 잘 통하는 '텅스텐'을 채워넣습니다. 전압을 거는 ‘게이트’를 만들기 위한 밑작업니다. (그림의 (c))

⑤ 게이트 모양으로 예쁘게 깎아내서(그림의 (d)) 개별 셀을 완성합니다. 각종 배선을 연결을 용이하게 하기 위해 가장자리를 계단 모양으로 깎아냅니다.

문제는 낸드 공정이 앞으로 더 어려워진단 겁니다. 데이터 폭증 시대에 대응하기 위해 셀이 늘어나야 하고, 단수는 높아져야 하지만 채널 홀은 1층부터 옥상까지 균일하고 반듯하게 뚫어내야 하니까요. 그 뿐 아닙니다. 낸드 칩 전체 면적을 줄이기 위해 주변 회로를 셀 옆자리에서 밑으로 옮기는 공정도 간과할 수 없습니다. 그럼 더 높이 쌓은, 더 많은 용량의 낸드를 구현하기 위해 어떤 차세대 기술이 고안되고 있는지 살펴봅시다.

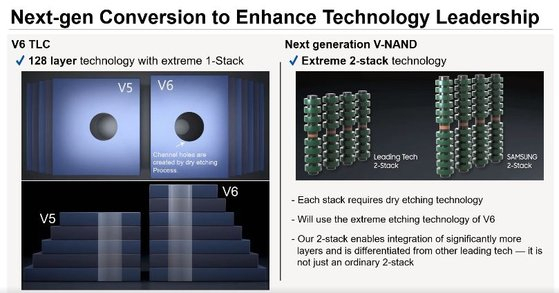

△더블스택 공정

가장 많이 알려진 공정 변화입니다. 200단 이상 낸드플래시 시대가 도래하면서 채널 홀을 한번에 파내는 것이 정말 힘들게 됐죠. 그래서 두 번(더블)에 나눠서 구멍을 뚫고 결합하는 이 공정이 대세입니다. 삼성전자는 최근 양산하는 7세대 176단 낸드는 '더블 스택' 공정을 활용하겠다고 밝혔죠. 다만 더블 스택 공정을 활용하면 채널 홀 만들기야 훨씬 수월해지겠지만 공정 단계가 복잡다단해진다는 단점이 있습니다. 비용이 증가하고, 공정 시간도 늘어난다는 얘긴데요.

그래서 소재 혁신도 중요합니다. 채널홀을 뚫기 전 절연막과 질화막 층을 100단 이상 차례로 쌓는 ②번 기초공사에서, 막 두께를 최대한 얇게 해서 채널홀을 되도록이면 한번에 뚫어보려는 시도도 주목해야 합니다.

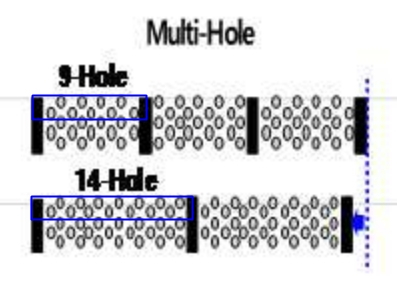

아, 채널홀 이야기가 계속 나와 잠깐 살펴보겠습니다. 채널홀 공정 혁신도 시도되고 있습니다. 삼성전자는 지난 4세대(64단) 낸드부터 '9-홀'이라는 독자적인 채널홀 구조를 쓰고 있습니다. 이제 이 구조를 업그레이드한 14-홀 공정을 연구 중인 것으로 파악됩니다. 같은 면적에 더 많은 구멍을 뚫어 용량을 높이려는 시도로 보입니다.

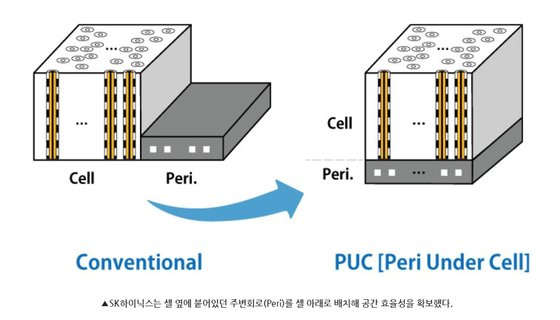

△주변회로(Peri.) 공정

낸드 안에는 셀만 있는 게 아닙니다. 이 셀들을 동작하게 만드는 주변부 회로(Periphery)가 있습니다. 최근 셀 옆에 있던 주변회로가 칩 면적 감소를 위해 셀 '밑'으로 들어가면서 공정 문제도 있을 것으로 보입니다. 이 경우 주변회로를 완성한 뒤, 바로 위에서 셀 공정을 시작하는데요. 마치 지하주차장을 완성하고 고층 건물을 쌓아올리는 방식이 되겠네요.

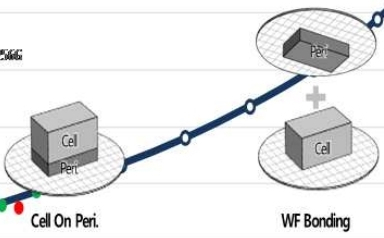

또 다른 방법으로는 주변 회로 공정과 셀 공정을 '아예' 따로 진행해서 하나로 이어 붙이는 '본딩' 방식도 개발되고 있습니다. 최근 반도체 업계에서는 이런 '이종접합' 패키징이 상당히 이슈죠. 중국 낸드업체 YMTC가 최근 낸드 공정에서 이 시도를 한 것으로 파악됩니다.

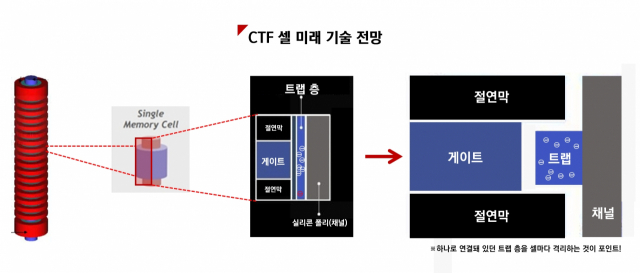

△CTF 혁신

현재의 채널홀을 보면 트랩 층이 각 셀마다 구분돼 있지 않고, 1층부터 100층 이상까지 하나로 길게 연결돼 있는 걸 보실 수 있습니다. 아무리 트랩 층이 절연체지만 전기 알갱이가 다른 셀로 도망갈 확률도 적지 않죠.

그래서 미래에는 이 트랩 층을 구분된 셀에 격리시키는 공정도 고안되고 있습니다. 이웃 셀 간 전기 알갱이가 섞여버릴 위험을 '원천 차단'하는 셈이죠. 하지만 공정 난도는 상당히 높습니다. 기존처럼 박막을 씌우는 '증착' 공정으로 끝나지는 않을 것으로 보이죠. 그림으로 차이점을 더 쉽게 관찰해보세요.

아울러 CTF 부분의 다양한 신소재 혁신으로 성능과 신뢰도를 높이는 연구도 활발히 진행되는 모습입니다.

이밖에도 낸드 혁신을 위한 다양한 공정이 논의되고 있는 상황입니다. QLC를 넘어 한 개 셀에 5개 이상의 비트를 저장할 수 있는 기술, 낸드플래시의 단점으로 꼽히는 △속도를 개선하면서 △CTF의 수명을 극대화할 수 있는 방법 등은 업계가 당면한 과제입니다.

◇사람이 곧 '미래'

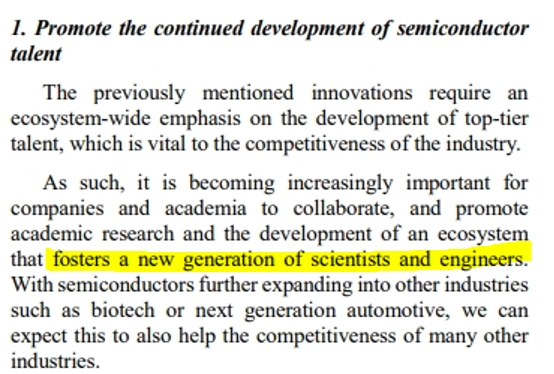

이런 혁신 기술을 해내는 것은 역시 사람이죠. 풍부한 '인력'이 있을수록 훨씬 더 좋은 기술이 나오는 것은 자명합니다. 김기남 회장도 이번 IEDM 기조연설에서 "학계와 업계 간 협력으로 새로운 과학자와 반도체 엔지니어를 키워내는 것이 상당히 중요해지고 있다"며 인력의 중요성을 언급한 바 있습니다.

하지만 국내 낸드 학계에서는 관련 연구나 인력 양성이 크게 지지부진한 것으로 알려져 있습니다. 유력 대학교에서도 학생들이 메모리, 특히 낸드플래시를 공부할 수 있는 강의를 찾기는 손에 꼽을 정도로 희귀하다고 하죠. 낸드 1위 국가에서 나타난 '모순점'입니다.

우리나라가 세계 최고의 메모리 기술을 확보하고 있지만, 다음 세대에서도 이 영향력을 그대로 유지하려면 현실에 안주하지 않는 적극적인 인력 확보와 학계 연구 지원이 필요하다는 목소리도 나옵니다.

김윤 서울시립대 교수는 "국내 학계에서 낸드플래시 전공 교과목이나 산업계와 협력한 교육 인프라가 매우 부족한 실정이며, 낸드 관련 연구도 많이 줄어든 상황"이라며 "낸드 기술을 활용한 인공지능 반도체 기술 개발 등 유망 연구 분야 발굴이 필요하다"고 밝혔다.

'쌓기 싸움'이 더욱 치열해지는 '다사다낸' 시대. 최고 낸드 기술 보유국으로서 내년에는 더 적극적인 국가 지원과 사람들의 관심이 이어지길 바라면서 글을 마무리합니다.

모두 새해 복 많이 받으세요.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >