삼성이 반도체 ‘초격차’ 회복을 위한 전제 조건인 차세대 D램 수율 개선 작업에서 의미 있는 성과를 거둔 것으로 확인됐다. 지난해 5월 복귀한 전영현 디바이스솔루션(DS) 부문장 부회장의 ‘설계 변경’ 이라는 초강수 대책이 빛을 발한 셈이다. D램은 인공지능(AI) 반도체 고대역폭메모리(HBM)의 핵심 재료인 만큼 삼성의 경쟁력 회복이 기대된다.

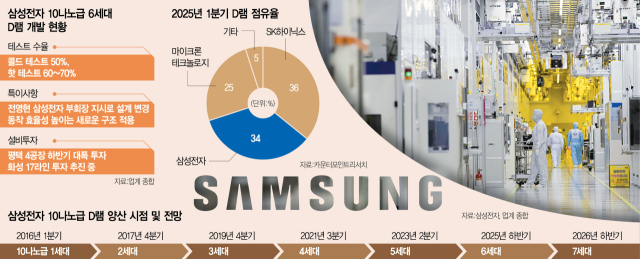

29일 업계에 따르면 이달 삼성전자(005930)는 10㎚(나노미터·10억분의 1m)급 6세대 D램 웨이퍼 성능 실험에서 의미 있는 수율을 달성했다. 차가운 환경인 콜드 테스트 수율은 50%, 뜨거운 조건의 핫 테스트 수율은 60~70%다. 웨이퍼 한장으로 1000개 이상의 D램을 만드는데 이 가운데 절반 이상의 D램 칩이 기준을 통과했다는 얘기다. 업계에서는 통상 수율 40% 안팎을 양산에 돌입할 수 있는 기준으로 보는데 이를 한참 웃돈 셈이다. 지난해 같은 제품의 수율이 채 30%에도 못 미쳤던 점을 고려하면 상당한 진전을 이뤘다.

비결은 설계에 있다. 삼성 연구진은 칩의 동작 효율성을 높이기 위해 다양한 구조를 새롭게 적용했다. 다만 설계 변경이 그렇게 간단한 일은 아니다. 스스로 잘못을 인정하는 꼴인 데다 그새 경쟁사들과 기술 격차가 벌어질 수 있고 상당한 자금을 쏟아부어야 한다. 애초 삼성전자는 지난해 말 10나노급 6세대 D램 양산을 계획했지만 설계 변경 시 스케줄이 1년 이상 늦춰질 수 있는 만큼 상당한 모험이었다.

2017년까지 메모리사업부장으로 있다가 7년 만에 돌아온 ‘올드 보이’ 전 부회장은 설계 변경만이 본원 경쟁력 회복을 위한 방법이라고 판단했고 1년이 지난 지금 그 결정은 조금씩 성공을 향해 가는 모습이다.

삼성전자는 연내 양산을 목표로 6세대 D램 후속 테스트를 진행할 계획이다. 업계 관계자는 “당장 판매를 해도 될 만큼 안정적인 성능을 갖췄는지 확인하려면 더 까다로운 테스트를 거쳐야 한다”고 전했다.

차세대 D램 개발 과정이 순조롭게 진행되면서 HBM에 대한 기대감도 높아지고 있다. HBM은 여러 개의 D램을 쌓아서 만든 칩이다. 5세대 HBM(HBM3E)에서 SK하이닉스(000660)에 1위를 빼앗긴 삼성전자는 업계 최초로 10나노급 6세대 D램을 쌓아 차세대 6세대 HBM(HBM4)을 연말까지 양산해 역전을 노리고 있다. 목표 시점 안에 제품을 만들려면 중요한 재료인 10나노급 6세대 제품의 완성도가 무엇보다 중요하다.

삼성전자는 차세대 D램과 HBM4 생산에 발맞춰 원가 경쟁력을 높이기 위해 대규모 설비투자도 진행할 방침이다. 최첨단 반도체 공장인 경기도 평택 4공장 위주로 하반기부터 제조 설비를 확충할 예정이다. 화성에 있는 D램 17라인도 공정 전환을 추진 중인 것으로 알려졌다.

삼성전자는 6세대에서 경쟁사에 밀린 과오를 만회하기 위해 10나노급 7세대 D램 개발도 동시에 진행하고 있다. 평택 2공장에 10나노급 7세대 D램 시험 라인을 설치했으며 연구개발(R&D) 단계에서 D램이 동작하는 워킹 샘플 제작을 완료한 것으로 알려졌다. D램 소자의 길이를 변경하는 등 개발 난도를 수정해 양산 시기를 앞당기는 전략을 펴는 것으로 전해졌다.

SK하이닉스가 삼성전자보다 먼저 10나노급 6세대 D램 개발을 완료한 가운데 삼성전자가 10나노급 7세대 D램 개발에서 역전에 성공한다면 반도체 ‘위기론’에서 벗어날 수 있을 것으로 보인다. 올 1분기 SK하이닉스에 내준 D램 시장 점유율 1위 자리도 되찾을 계기가 마련될 수 있다. 업계 관계자는 “이르면 내년 하반기 중 7세대 양산을 목표로 개발하는 것으로 알고 있다”고 말했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >