세계 최대 파운드리(반도체 위탁 생산) 업체 대만 TSMC가 2026년 하반기부터 1.6㎚(나노미터·10억분의 1m)급인 ‘A16’ 공정을 통한 반도체 생산에 들어갈 계획이라고 밝혔다.

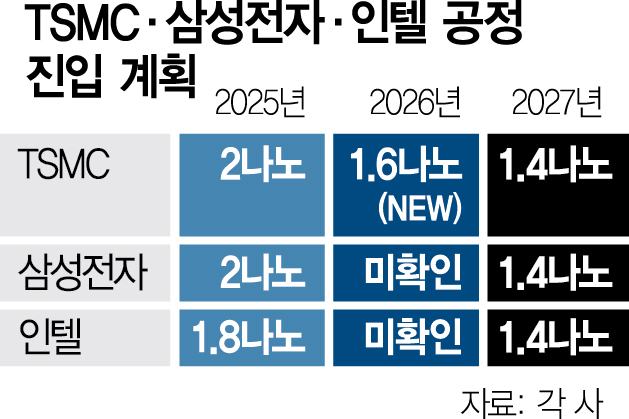

2025년과 2027년 각각 돌입 예정인 2나노와 1.4나노 사이에 가교를 두겠다는 전략으로 해석된다. 반도체 파운드리에 복귀한 인텔이 TSMC·삼성전자(005930)보다 한 박자 빠른 초미세공정 로드맵을 제시한 가운데 TSMC가 공정 세분화로 적극 대응하고 나선 양상이다.

TSMC는 미국 캘리포니아 샌타클래라에서 북미 기술 심포지엄을 열고 A16 공정 계획을 공개했다.

YJ 미이 TSMC 최고운영책임자(COO)는 “새로운 칩 제조 기술인 A16이 2026년 하반기 생산에 들어간다”며 “해당 공정은 반도체 칩 뒷면에서 전력을 공급할 수 있어 속도를 높일 수 있다”고 강조했다. 인텔 ‘파워비아’와 유사한 후면전력공급(BSPDN) 방식을 도입하겠다는 뜻으로 읽힌다.

TSMC와 삼성전자는 2025년 2나노, 2027년 1.4나노 도입을 목표로 삼고 있다. TSMC는 2나노와 1.4나노 간의 간격이 큰 만큼 그사이에 1.6나노 공정을 끼워넣은 것이다. TSMC의 1.6나노 가교 전략은 인텔의 초미세공정 공세에 대응하기 위한 조치로 해석된다. 파운드리에 복귀한 인텔은 당초 4년간 5개 공정에 진입해 2025년에 1.8나노급(18A)에 도달하겠다는 ‘4Y5N’을 당초 제시했는데 이를 앞당겨 올해 말께 달성하겠다고 밝혔다. 미세공정 경쟁에서 TSMC와 삼성전자를 제친다. 인텔은 이어 ASML로부터 도입한 하이NA 극자외선(EUV)을 바탕으로 2027년까지 1.4나노급(14A)에 돌입하겠다는 목표도 내놓았다.

TSMC는 1.4나노 공정 도입이 인텔보다 늦어질 가능성에 대비해 1.6나노로 초미세공정 반도체 수주를 선점하겠다는 전략인 것으로 해석된다. 1.4나노 진입에 필수적인 ASML 하이NA EUV 수급이 어렵다는 현실적인 이유도 작용하고 있다.

케빈 장 TSMC 비즈니스개발담당 수석부사장은 “이름을 밝힐 수 없는 AI 반도체 회사 수요로 인해 새로운 A16 제조 공정을 개발했다”며 “A16 공정에는 하이NA EUV를 사용할 필요가 없다고 생각한다”고 설명했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

beherenow@sedaily.com

beherenow@sedaily.com