독자님, 안녕하세요. '삼성전자(005930) 12나노급 D램에 관한 7가지 흥미로운 이야기' 2편입니다.

1편에서는 D램의 역할과 생산성, 전력 효율성에 대해서 살펴봤습니다. 2편에서는 신규 D램의 속도 계산법, DDR5와 EUV, 커패시터에 대해 알아보겠습니다.

4. 이번 제품은 최대 동작속도 7.2Gbps를 지원한다. 이는 1초에 30GB 용량의 UHD 영화 2편을 처리할 수 있는 속도이다.

이번 제품 동작 속도에 대한 이야기부터 시작해보겠습니다. 7.2Gbps가 대체 뭘까. Gbps는 '초당 기가비트(Gigabit Per second)'입니다. 위에서 비트는 데이터의 최소 단위이고, 기가(G)는 대략 10억이라고 설명드렸죠. 네. 7.2Gbps는 7.2X10억, 그러니까 D램 속 약 72억개 기억 공간에 있는 0 또는 1을 단 1초만에 동시에 빼거나 집어넣을 수 있다는 얘깁니다.

뒤에 나오는 기가바이트(GB) 중 바이트는 데이터 한 묶음의 단위입니다. 1바이트는 8개의 0또는 1(비트)로 이뤄진 일종의 정보 꾸러미입니다. ‘00000000’부터 ‘11111111’까지. 2의 8승, 1바이트에는 총 256가지 경우의 수가 나오겠네요.

아무튼 그래서 간략하게 비트와 바이트 관계를 정리하면 '8비트(b)=1바이트(B), 또는 1비트= 0.125바이트'입니다.

오, 근데 자료만 보면 조금 이상한 계산이 나옵니다. 7.2Gb를 1초에 전송한다…'1비트=0.125바이트' 식에서 양변에 7.2를 곱하고 G를 갖다붙이면 초당 0.9GB 데이터만 전송하는 거 아닌가? 어떻게 60GB(30GB 영화 2편)이라는 값이 나올까.

궁금해서 좀 더 알아봤습니다. 그랬더니 여기선 두 가지 더 설명할 게 있었습니다. 먼저 '핀(Pin)'의 개념입니다. 핀은 D램 속 정보가 안팎으로 왔다갔다 할 수 있는 통로입니다. 회사·학교 입출구(I/O)와 엘리베이터로 이해하면 쉽습니다. 이번에 개발한 D램 속에는 8개 핀이 탑재됐다고 합니다. 이 핀당 데이터 처리 속도가 7.2Gbps라고 합니다. 두 번째, 이 계산은 이번 12나노 급 D램 모듈 단위로 봐야 합니다. 이번 제품에는 한 모듈 당 8개 D램이 장착됐다고 해요. 그러니 1개 D램 칩이 아닌, 1개 모듈 속 8개 D램 칩이 합심해서 영화를 처리한 속도를 계산한다고 봐야 합니다. 그러니까 복잡하지만 다시 정리해보면

7.2(Gb에서 출발) X 0.125(GB 단위로 환산 완료) X 8(핀 수 계산 완료) X 8(모듈 당 D램 개수 계산 완료) = 57.6. 거의 60GB에 가까운 값이 나오게 되네요. 핀과 모듈의 존재감을 잊지 말아야 할 것 같습니다.

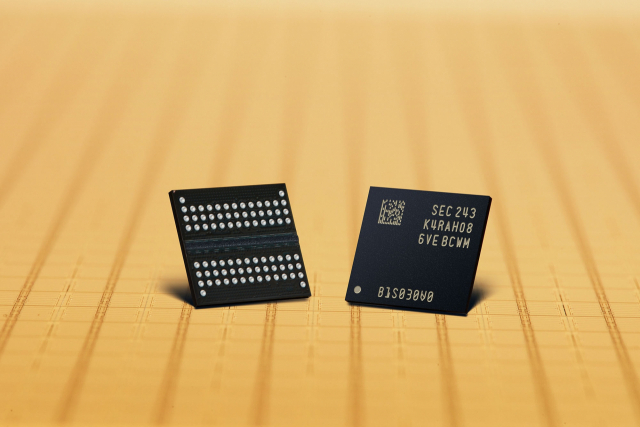

5.업계 최초 12나노급 16Gb "DDR5 D램" 개발

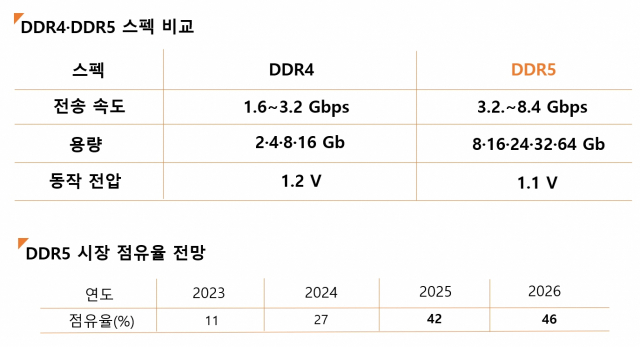

DDR5라는 용어는 이미 언론 기사에서도 참 많이 다뤄져서 간략하게만 설명하겠습니다. DDR5는 D램 회사와 각종 IT 업체들이 정한 D램 규격입니다. 지난 2013년 DDR4가 지정된 데 이어 2020년엔 DDR5가 제정됐습니다. AI, 가상현실, 클라우드 시대로 데이터가 폭발하니까 "고도화한 D램 스펙을 '표준화'해서 전자부품·기기 업체들이 수월하게 D램을 호환할 수 있도록 해보자"고 만든 게 DDR5입니다. 다양한 D램 회사들은 통상 이 규격 안에서 칩을 만들게 됩니다. 한 예로 이번에도 삼성은 DDR5 규격에 맞춰 16Gb D램을 냈죠. 32, 64Gb 개발도 조만간일 듯 합니다.

표에서 보실 수 있듯 전반적으로 전송 속도와 용량이 쭉쭉 늘어났고, 동작 전압은 낮춘 것이 특징입니다(부피 축소가 주요 원인으로 추론할 수 있죠?). 내년부터 인텔 등 글로벌 프로세서 회사가 DDR5가 호환되는 CPU를 생산하면서 D램 업계도 새로운 전환점을 맞게 됐죠. D램 불황기로 침체된 분위기 속에서 과연 DDR5가 역전의 키워드가 될 수 있을지 지켜봐야겠습니다. 향후 DDR5의 점유율도 시장조사업체 옴디아의 전망치를 참고해주세요.

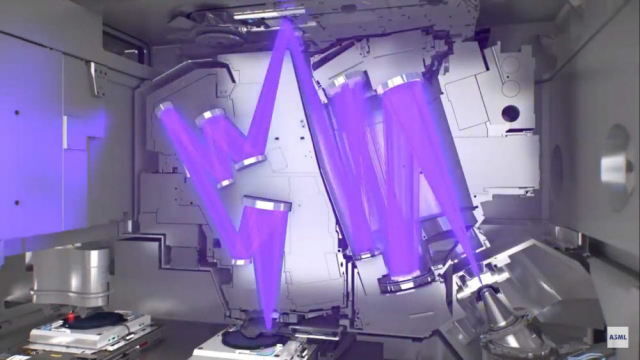

6. 멀티 레이어 EUV 기술을 활용해 업계 최고 수준의 집적도로 개발됐다.

EUV 역시 참 많이 언급되는 이야기이죠. 삼성전자는 14나노 D램을 12나노급으로 줄일 수 있었던 핵심 기술로 EUV를 소개했습니다. EUV는 반도체 회로 모양을 빛으로 찍어내는 노광 공정에서 활용되는 광원(光源)입니다. 기존 불화아르곤(ArF) 빛보다 파장이 14분의 1 짧아서 얇은 회로를 더 정교하고 반듯하게 찍어낼 수 있죠.

삼성전자는 2021년 10나노 1세대(게이트 폭이 10나노 후반대인) D램에 EUV를 첫 적용한 이후 점차 확대 중입니다. 실제 전작인 14나노 D램에선 5개 레이어(알려지기로는 D램 레이어는 총 50~60개로 구성됐다고 합니다)에 EUV가 쓰인 것으로 전해지고요. 이번엔 더 발전해 5개 이상의 회로 공정에 EUV가 활용됐을 것으로 보입니다.

SK하이닉스도 이미 EUV 기술로 D램을 만들고 있고, 미국 마이크론 테크놀로지도 EUV 도입을 준비하고 있습니다. D램 업체들의 EUV 활용 전략도 향후 D램 업계의 상당한 이슈가 될 것 같습니다.

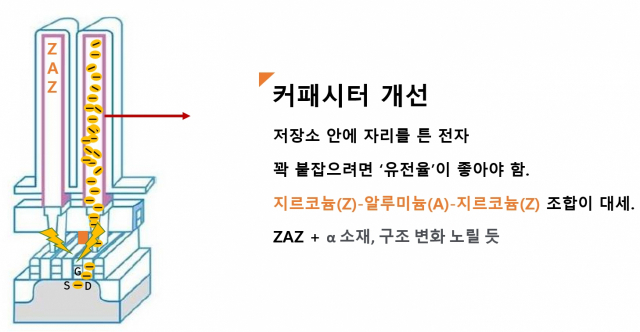

7. 삼성전자는 유전율(K)이 높은 신소재 적용으로 전하를 저장하는 커패시터(Capacitor)의 용량을 높였다.

마지막 이야기입니다. '기억의 공간' 속 커패시터 얘기를 해보려고 합니다. D램에서는 트랜지스터의 대문인 '게이트'에 전압이 걸리고, 통로(채널)가 개방되면 전기 알갱이들이 질주해 들어가면서 커패시터로 쏙 들어가 자리를 틀게 되죠. 커패시터가 저장하고 있는 전하 종류에 따라 디지털 신호가 0 또는 1로 구분됩니다. 따라서 커패시터 성능은 굉장히 중요합니다. D램은 특성 상 전기 알갱이가 언제든지 도망나갈 수 있는 메모리라서요. 만약 전기 알갱이가 커패시터로 들어왔다면 못 도망가게 잘 움켜잡아야 합니다. 잡아야 할 것을 놓치는 순간 문제가 생기는 겁니다.

그래서 커패시터 내부에는 유전(揄電·끌어들일 유, 전기 전)율이 높은 물질, 즉 전기 알갱이들을 잘 끌어들여서 꽉 붙잡을 수 있는 소재로 도배를 해놓습니다. 이 커패시터 막의 유전율은 갈수록 중요해지고 있습니다. 기억의 공간 면적이 줄어들면 커패시터의 크기도 줄어들고 유약해지기 마련이죠. 몸집이 줄어들면 유전율이 큰 소재라도 채워놓아야 예전에 발휘했던 카리스마를 발휘할 수 있습니다. 지금까지 커패시터 유전막은 유전율이 좋은 소재 조합으로 알려진 지르코늄-알루미늄-지르코늄(ZAZ) 층으로 만들어졌는데요. 업계에 따르면 이 ZAZ 조합에 좀 더 다양한 물질을 배합해서 유전율을 높이기 위한 방법을 칩 제조사에서 고안해내고 있다고 합니다. 커패시터 소재 기술. 어디까지 진화할까요?

지금까지 삼성전자 12나노 D램 보도자료를 자세히 뜯어봤습니다. 사실 내용이 너무 생소하고 쉽지 않지만, 앞으로 나올 D램 기술의 변화 포인트를 짚어보는 것도 큰 재미인 것 같습니다. 내년 D램 기술 시장에서는 과연 어떤 일이 벌어질 지 기대하면서 이번 연재물 마무리합니다. 독자 여러분, 올해도 정말 고생 많으셨습니다. 내년에 더 좋은 내용으로 찾아뵙겠습니다. :)

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >