삼성전자가 고대역폭메모리(HBM)를 넘어서는 차세대 D램 기술을 개발하고 있다. 또 파운드리(반도체 위탁 생산) 분야의 최대 라이벌 TSMC를 추격하기 위해 내년에도 2조 원 이상을 패키징 라인 확충에 투자하기로 했다.

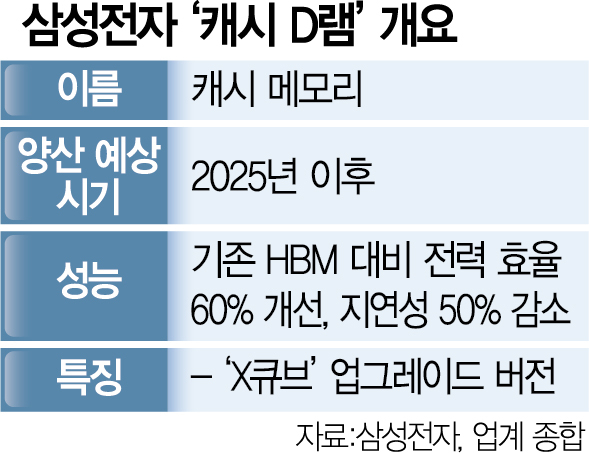

5일 반도체 업계에 따르면 삼성전자 어드밴스드패키징(AVP)사업팀은 일명 ‘캐시 D램’ 기술 개발에 뛰어들었다.

캐시 D램은 최근 업계를 강타한 HBM를 한 단계 업그레이드한 것이다. HBM은 여러 개의 D램을 한 개의 칩처럼 수직으로 쌓아 고용량을 구현하는 반면 캐시 D램은 단 한 개의 칩으로 HBM과 맞먹는 정보를 저장할 수 있다. 이르면 2025년 양산을 목표로 개발 중인 것으로 알려졌다.

캐시 D램은 HBM을 패키징할 때와 방법이 다르다. 현재 HBM은 그래픽처리장치(GPU) 옆에 수평으로 연결된다. 반면 캐시 D램은 프로세서 위에 수직으로 자리 잡아 연결된다. 이렇게 칩을 최대한 붙여서 배열하면 전기적으로 더 많은 정보를 처리하기가 쉬워지고 가격 경쟁력도 높일 수 있다. D램을 쌓아올리면서 생기는 발열을 잡는 것이 향후 해결해야 할 가장 큰 과제로 보인다. 삼성전자 측은 “캐시 D램이 상용화될 경우 기존의 HBM보다 전력효율은 60% 개선되고 정보 이동 지연성은 50% 감소하는 효과를 거둘 것”이라고 설명했다.

한편 삼성전자는 캐시 D램 외에도 반도체 핵심 분야로 떠오른 첨단 패키징 기술을 실현하기 위해 불황임에도 올해 18억 달러(약 2조 원) 이상의 대규모 투자에 나설 것으로 예상된다. 또한 자사 반도체 제조뿐 아니라 파운드리 분야에서 반도체 ‘큰손’들을 유혹하기 위한 3㎚(나노미터·10억분의 1m) 칩 패키징 기술 개발에도 열을 올리고 있다. 올해 AVP팀을 신설해 TSMC 등 라이벌 회사의 고급 패키징 기술을 바짝 추격하는 모습이다.

반도체 업계의 한 관계자는 “미세 회로 구현이 점차 힘들어지면서 각종 칩을 이어붙이는 3D 패키징이 칩 회사들의 경쟁력을 가르는 분수령이 될 것”이라며 “삼성전자가 2030년 시스템반도체 1위 비전을 실현하려면 패키징 투자는 필수”라고 말했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >