|

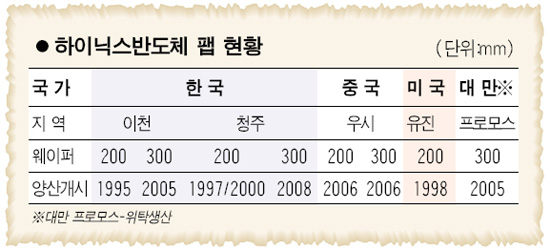

하이닉스 54나노 D램기술 대만 프로모스에 이전 추진 당초 66나노 이전계획 바꿔日업체와 제휴막기 포석 인 듯하이닉스 "기술유출은 아니다" 이규진 기자 sky@sed.co.kr 하이닉스반도체가 대만의 프로모스에 54나노 D램 공정기술 이전을 추진한다. 이는 최근 프로모스가 일본 엘피다와 손잡으려는 움직임에 제동을 걸기 위한 포석으로 풀이된다. 하이닉스가 60나노 공정기술을 빨리 이전하지 않자 이에 불만을 품은 프로모스는 제휴선을 변경하려는 움직임을 보여왔다. 이에 앞서 또 다른 대만 업체인 난야는 독일 키몬다와의 협력관계를 청산하고 미국의 마이크론과 기술공유와 함께 50나노 기술 개발에 나서기로 해 D램 업계에 재편 바람이 불고 있는 상황이다. 6일 관련업계에 따르면 하이닉스는 전략적 제휴를 맺고 있는 대만의 프로모스에 54나노 공정을 적용한 D램 생산기술을 이전하기 위한 협상을 벌이고 있다. 업계의 한 관계자는 “당초 66나노 기술을 이전할 계획이었지만 프로모스가 54나노를 강력 희망하고 있는 것으로 알고 있다”고 설명했다. 이에 대해 하이닉스의 한 관계자는 “업계에서 볼때도 확인해줄 수 없다”면서도 “54나노 공정기술은 올 3ㆍ4분기를 전후해 양산되기 때문에 만일 이전할 경우 그 시기는 1년 뒤가 될 것”이라고 말했다. 그는 또 “1년 뒤면 54나노 기술은 범용화된다”며 “기술유출이 아니다”고 덧붙였다. 하이닉스는 지난해 프로모스에 66나노 공정기술을 이전하기로 했으나 협상 타결이 안돼 기술이전에 차질을 빚어왔다. 하이닉스는 지난 2003년부터 프로모스에 로열티를 받고 D램 공정기술을 제공하고 생산량의 절반가량을 가져다 판매해왔다. 업계에서는 하이닉스와 프로모스 간 기술이전 대상이 66나노에서 54나노로 바뀐 것은 삼성전자가 2ㆍ4분기 내에 50나노를 양산하는 상황에서 66나노 공정기술의 실효성이 없다고 판단했기 때문으로 보고 있다. 현재 프로모스는 80나노 공정으로 D램을 생산하고 있다. ‘1억분의 1m’를 의미하는 나노는 회로선폭을 나타내는 미세공정 단위로 수치가 낮을수록 한 장의 웨이퍼에서 생산할 수 있는 칩 수가 많아진다. 일반적으로 80나노급 공정에 비해 60나노급 공정의 생산성이 2배 높고, 60나노급 공정에 비해 50나노급 공정은 50% 이상의 생산성 향상이 가능하다. 한편 지난해 8월 말 발효된 산업기술유출방지법에 따르면 D램의 경우 80나노 이하의 설계부터 조립 검사 기술을 해외로 내보낼 때는 지식경제부에 신고해야 한다. 만약 ‘국가안보에 심각한 영향’을 줄 경우 산업기술보호위원회의 의결을 거쳐 수출중지·수출금지·원상회복 등을 명령할 수도 있다. 이를 근거로 업계 일각에서는 하이닉스의 나노 공정기술 이전으로 기술이 유출될 수 있다며 엄격한 심사를 요구해왔다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >