삼성전자가 고급 반도체 패키징 기술을 뽐내며 파운드리(칩 위탁생산) 경쟁력을 과시했다. 세계 파운드리 1위 업체 TSMC와 경쟁하기 위한 첨단 칩 설계 기술과 삼성전자가 구축 중인 자체 파운드리 생태계 'SAFE'의 장점도 강조했다.

18일 삼성전자는 'SAFE 포럼 2021'을 온라인으로 개최하고 '퍼포먼스 플랫폼 2.0'이라는 주제로 회사 파운드리 비전과 경쟁력을 알렸다. 이날 기조연설자로 나선 이상현 삼성전자 파운드리사업부 전무는 혁신, 지능, 집적 등 3개의 큰 축으로 퍼포먼스 플랫폼 2.0이 실행될 것이라고 밝혔다.

특히 이 전무는 '결합(integration)', 즉 반도체 패키징 솔루션을 소개하는 데 많은 시간을 할애했다.

반도체 패키징은 칩을 포장하는 작업이다. 칩과 메인보드 간 연결을 돕고, 열과 습기 등을 차단하는 부품과 소재를 장착하는 것이 주요 미션이다. 한 개 칩(다이)을 만드는 전(前)공정 뒤에 이뤄져 후(後)공정이라고도 불린다.

하지만 최근에는 패키징 기술이 전공정만큼 고도화하고 있다. 완성된 다이를 이어 붙여 한개 칩으로 만들거나, 다이 옆에 전혀 다른 종류의 다이를 붙여 한 개 반도체처럼 동작하게 하는 '이종접합' 콘셉트가 유행하고 있다. 집적도 개선이 한계에 다다르고 있지만 칩 성능은 더욱 높아져야 하는 상황을 마주한 반도체 설계 회사들은 이 기술에 상당히 주목하는 추세다.

삼성전자가 '결합'을 핵심 포인트로 내세우며 올해 포럼에서 유독 패키징을 강조한 이유도 여기에 있다. 반도체 설계도를 물리적 칩 모양으로 만들어내야 하는 삼성 파운드리가 칩 설계 고객사 고민에 즉각 대응하기 위해 최첨단 솔루션을 전면 제시한 것이다.

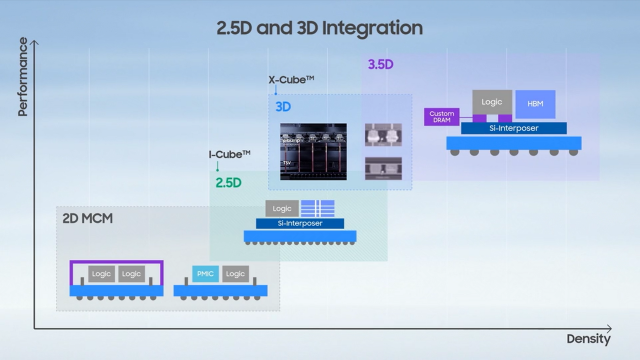

이 전무는 현재 구현하고 있는 로직 반도체와 고대역폭메모리(HBM)를 평평한 판(인터포저) 위에 얹는 2.5D(아이-큐브) 패키지, 최신 극자외선(EUV) 공정으로 만든 로직 다이 위에 메모리(SRAM)를 얹는 3D(엑스-큐브) 패키징 기술을 소개했다. 특히 이 로드맵에서 주목할 만한 것은 삼성전자의 3.5D 패키징이다.

이 전무는 엑스-큐브 공정으로 단순히 연산 장치 위에 S램을 얹는 수준을 넘어, 고객사 맞춤형 초고성능 메모리(커스텀 메모리)를 밀착시켜서 결합한다는 것을 나타낸 장표를 공개했다. 메모리와 연산 장치의 결합 대신 연산장치와 연산장치 결합, 지금껏 삼성전자가 후공정에 적용하지 않은 하이브리드 본딩 등 고도화 결합 공정이 활용될 것으로 예상된다.

또 이 전무는 ISC(Integrated Stack Capacitor)라는 패키징 기술도 일반 대중에게 첫 공개했다. ISC는 칩의 전류와 전압 흐름을 제어하는 '캐패시터'를 2.5D 및 3D 패키징에 활용하는 인터포저 안쪽으로 끌어들인 혁신 기술이다.

기존에는 이 캐패시터가 인터포저 바깥에 칩 모양으로 장착되는 방식이었다. 무라타, 삼성전기 등이 이 캐패시터를 만들어서 공급한다. 하지만 ISC 기술로 인터포저 안에 캐패시터를 집어 넣으면 전류의 흐름을 바깥에 있을 때보다 훨씬 효율적으로 제어할 수 있고 실장 면적도 줄어든다.

물론 바깥에 위치한 캐패시터보다 면적이 작아 한번에 처리할 수 있는 전류의 양은 적지만 2.5D, 3D 패키징이 요구하는 빠른 정보 처리에는 큰 장점을 가지고 있는 것으로 전해진다. 이런 패키징 공정을 구현하기 위해 삼성전자는 자신들이 꾸린 SAFE 생태계 안에 ASE, 앰코, 하나마이크론, 네페스 등 10개 후공정(OSAT) 파트너들이 있다고 소개했다.

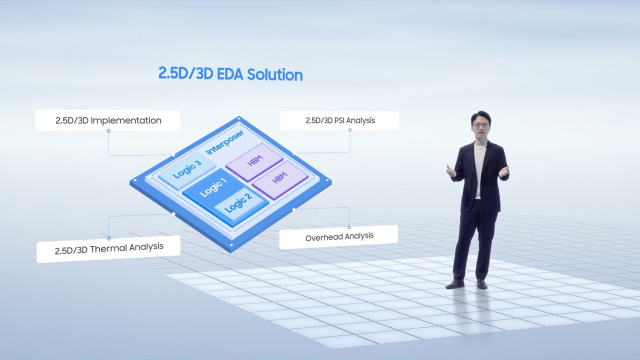

이 전무는 삼성 파운드리가 공정 기술 뿐 아니라 칩 설계 과정에서도 2.5D, 3D 패키징 디자인 툴을 확보하고 있다고 밝혔다. 관련 설계자동화툴(EDA) 솔루션 및 설계 자산(IP)을 일찌감치 확보하고, SAFE 생태계 내에서 삼성 파운드리 협력사와 함께 개발 중이라고 설명했다.

이 전무는 "다양한 2.5D·3D 패키징 기술로 ‘비욘드 무어’를 지향한다"고 밝혔다.

한편 이날 이 전무는 패키징 기술 외에도 3나노 게이트올어라운드(GAA) 기술, 80개 이상의 EDA 툴, 통합 클라우드 설계 플랫폼 등을 소개하며 SAFE 생태계의 장점을 강조했다.

이 전무는 "데이터 중심 시대로의 전환이 가속화되며, 높아지는 고객의 요구에 대응하기 위한 삼성전자 에코시스템도 함께 발전하고 있다"며 "업그레이드된 '퍼포먼스 플랫폼 2.0' 비전 실현을 주도해 나가겠다"고 밝혔다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >