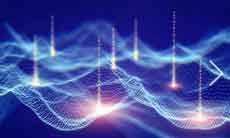

인텔이 반도체 뒷면에서 전력을 공급하는 새로운 구조의 소자를 구현했다. 복잡한 제조 공정을 간소화하고 칩 동작 오류를 줄일 수 있는 이 기술로 반도체 리더십을 고수한다는 전략이다.

인텔은 반도체 소자 뒷면에서 전력을 공급하는 '파워비아' 기술을 테스트 칩에 구현했다고 6일 밝혔다. 칩의 뒷면에 전력 공급 장치를 단 것은 인텔이 세계에서 처음으로 시도했다.

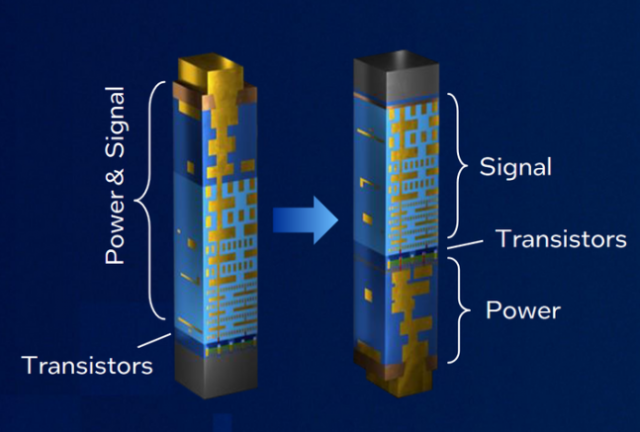

통상 반도체 속 연산 장치로 전력을 공급하는 배선은 전면부에 있었다. 이러한 구조는 반도체 회로가 미세화할 수록 문제가 됐다. 통상 반도체 칩 안에서 디지털 신호와 전력 공급은 같은 회로에서 이뤄졌다. 이 회로가 점점 얇아지면서 전력 전달 속도가 느려질 뿐만 아니라, 디지털 신호와 전력 공급이 섞여 불필요한 간섭현상을 만들어냈다. 배선 당 부담을 분산하기 위해 개수를 늘리면 공정이 복잡해져서 비용이 증가한다.

인텔은 이런 문제를 해결하기 위해 디지털 신호 전달 회로와 전력 공급 배선을 구분했다. 분리한 전력 배선은 칩 뒤에 배치했다. 이 콘셉트가 '파워비아'다.

파워비아는 장점이 상당히 많다. 우선 전력 배선을 연산 장치(트랜지스터)에 바로 연결할 수 있는 점이 좋다. 원하는 전력을 연산 장치로 바로 배달할 수 있다는 것이다. 또 신호 회로와 분리돼 있어 간섭 현상이 발생할 가능성도 0%다.

인텔은 메테오 레이크 E코어에 '파워 비아'를 적용한 테스트칩을 만들었다. 실험 결과 코어(연산 장치)의 속도가 6% 향상했고, 패키징 단계에서 전력 공급 문제(드룹·droop)가 30% 이상 해소됐다. 인텔 관계자는 "전력과 관련한 안전성 문제를 유발하지 않고도 성능 개선을 달성할 수 있었다"고 설명했다.

인텔은 향후 20A(2나노미터급) 공정으로 만드는 반도체 칩에 파워비아 기술을 적용할 예정이다. 차세대 트랜지스터 구조인 '리본펫' 등과 함께 활용할 것으로 보인다.

벤 셀 인텔 기술개발부문 부사장은 "후면 전력 공급 기술을 경쟁사보다 먼저 확보했다"며 "2030년까지 단일 칩에 1조개 트랜지스터를 탑재하겠다는 목표에 가까이 다가가는 주요 기술이 될 것"이라고 자신했다.

인텔은 이 연구 결과를 일본 교토에서 11일부터 16일까지 열리는 세계 3대 반도체학회 'VLSI 심포지엄 2023'에서 발표할 예정이다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com