지난 9일 국내 최대 반도체 전시회인 '세미콘 코리아 2022' 전시회가 개막했습니다. 김형섭 삼성전자 반도체연구소장(부사장)의 기조 연설과 함께 막을 올렸는데요.

이날 김 부사장은 '데이터 시대에 대응하는 실리콘 혁신'이라는 주제로 연설을 진행했습니다. 초연결 시대에 일어나는 데이터 폭증에 대응하는 차세대 반도체 기술 트렌드를 소개해 많은 청중의 관심을 끌었죠. 반도체 전방위 분야에 걸친 미래 기술과 전망이 발표 내용에 녹아 있었습니다.

반도체 분야 취업 준비·투자를 하시면서 기술에 관심이 생긴 독자분들께 이번 기조 연설 발표 내용을 공유 드리면 좋을 것 같아서 준비했습니다. 칩 구조 변화부터 정리해보겠습니다.

◇칩 별 구조 변화

김 부사장은 삼성전자가 현재 만들고 있는 반도체들의 구조 변화와 전망을 개괄적으로 설명했습니다. 삼성전자 주력인 D램, 낸드플래시 등 메모리 반도체부터 이미지센서, 시스템 반도체 구조와 미래까지 개괄적으로 조망한 점이 눈에 띕니다. 그가 소개한 기술 동향과 미래 기술을 차근차근 살펴 봅시다.

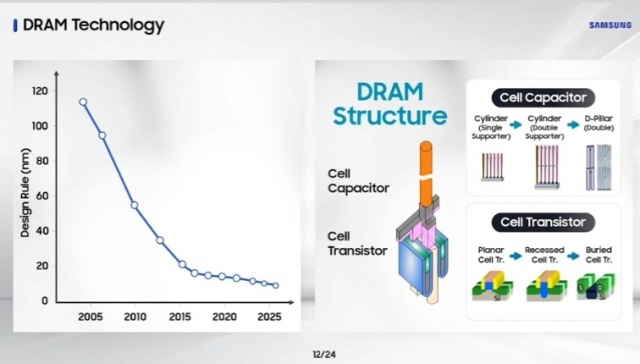

△D램

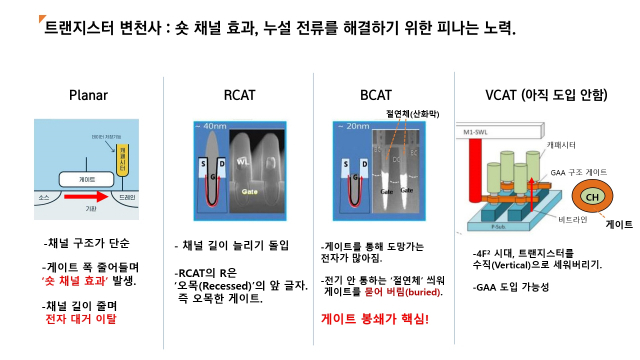

D램은 0 또는 1, 디지털 신호를 저장하는 공간인 셀 영역 구조 변화에 대한 설명이 주를 이뤘습니다. 칩 미세화로 인한 누설 전류(숏 채널 효과)를 해결하기 위해 부단하게 트랜지스터 모양을 변화시킨 사례가 주목됩니다.

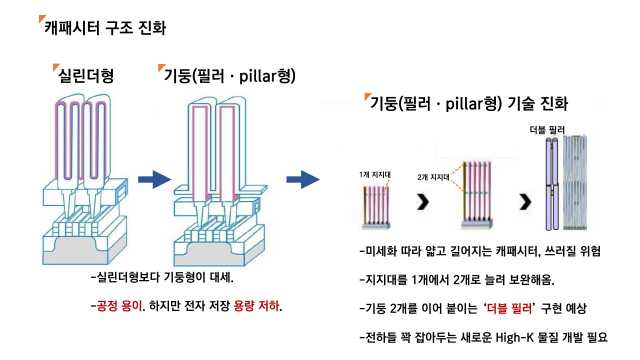

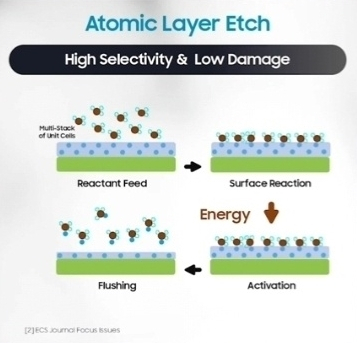

셀로 들어온 전기 알갱이(데이터)를 저장하는 ‘커패시터’의 용량 문제를 해결하기 위한 다양한 구조 변화도 언급했습니다. 김 부사장은 "좁은 영역에 높은 용량을 구현하기 위해 초고층 형태 구조를 만들기 시작했다"고 설명했습니다.

실제 가늘고 긴 커패시터를 지지하기 위해 두 개의 지지대를 사용하거나, 아예 커패시터 두 개를 이어붙이는 '더블 필러'가 고안되고 있습니다.

또 커패시터를 만들 때, 저장된 전기 알갱이들을 최대한 꽉 잡아둘 수 있는 물질(High-K·고유전체)을 개발해 제품 세대 별로 바꾸고 있다는 설명도 덧붙였습니다.

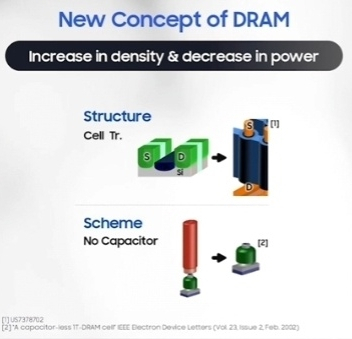

파격적인 차세대 D램 구조도 설명했습니다. 기존 평면 트랜지스터 형태를 넘어, 기둥 모양의 수직 트랜지스터(Vertical CAT)로 트랜지스터 수를 획기적으로 늘리는 방법, 커패시터 용량이 계속 문제가 되니 아예 캐패시터를 없애면서 집적도를 더 올리는 방안 등이 소개됐습니다. 아래 그림을 참고해주세요.

△낸드플래시

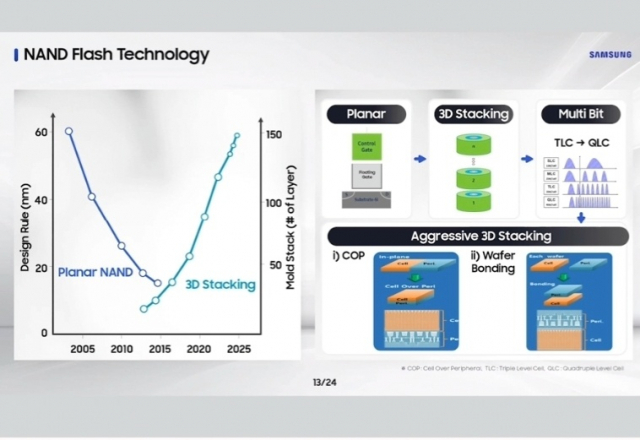

삼성전자는 2013년 평면 낸드플래시에서 수직 구조의 V낸드를 세계 최초로 양산한 회사이기도 하죠. 176단 낸드 양산까지 성공한 삼성전자는 지속 단수를 높여가며 업계 리더십을 가져가고 있습니다. 올해 삼성전자가 200단 이상 낸드플래시를 양산할지도 주목됩니다.

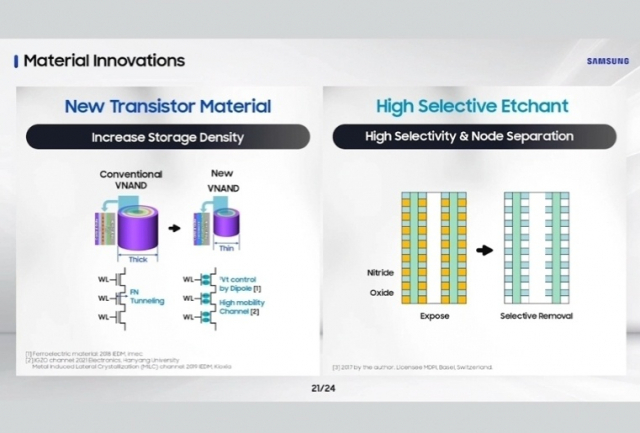

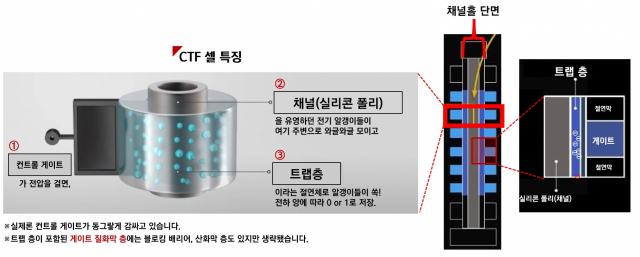

김 부사장은 미래 낸드플래시 기술을 짚으면서 공정에 활용되는 '소재' 혁신의 중요성을 강조했습니다. 그는 '트랩층' 소재 혁신이라는 이야기를 했는데요.

트랩층은 차지트랩플래시(CTF) 방식 3D 낸드플래시에서 전원이 꺼지더라도 전기 알갱이들을 꽉 묶어서 정보를 저장하는 공간이죠. 낸드플래시 정보 저장의 핵심 영역입니다.

김 부사장은 지금보다 전기 알갱이들을 훨씬 세게 꽉 잡아둘 수 있는 트랩층을 개발하려는 시도가 지속되고 있다고 소개했습니다. 강유전체(Ferroelectric) 콘셉트가 그것입니다. 전기 알갱이를 기존보다 강(强)하게 끌어들이는 부도체이자 강유전체인 트랩용 물질을 찾고 있다는 거죠.

이렇게 전자를 강하게 끌어들이는 물질은 쓰면 낸드 전력 효율 증가를 모색할 수 있습니다. 더 낮은 전압을 셀에 걸어도, 자유분방한 전기 알갱이들이 알아서 강유전체의 힘에 이끌려 저장되는 것이니까 전력을 아낄 수가 있고요. 그러면 자연스럽게 전압을 거는 '게이트' 면적까지 줄일 수 있으니까, 같은 면적에도 단수를 더 쌓을 수 있는 기회까지 주어집니다. 트랩층이 있는 채널 홀 부피까지 줄일 수 있어 칩 내 더 많은 저장 공간을 만들 수도 있겠네요.

현재 트랩층은 전기가 잘 통하지 않는 ‘절연체’ 질화규소(SiN) 물질로 만들어지는 것으로 알려집니다. 앞으로 어떤 신소재가 트랩층의 주인공이 될지 지켜보는 것도 흥미로운 포인트가 될 것 같습니다.

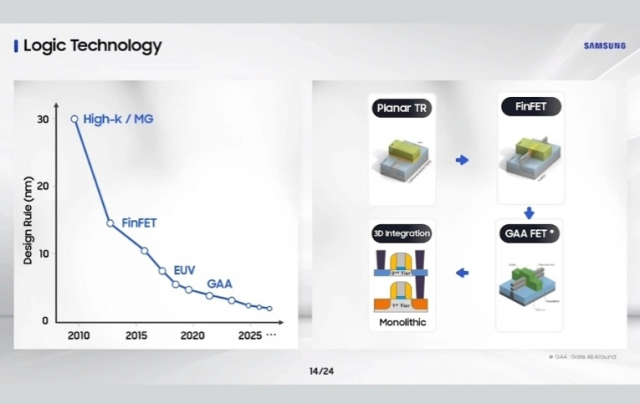

△로직 반도체

CPU, AP 등 전자 기기 두뇌 역할을 하는 로직 반도체는 고유전체 소재를 활용한 게이트 개선(High-K 메탈 게이트·HKMG), 전류가 더 빠르게 흐를 수 있는 배선, 최근 대세로 떠오른 게이트올어라운드(GAA) 트랜지스터 등을 적용해 미세화를 이어오고 있죠.

김 부사장은 전력 효율화를 위한 구조 변화가 로직 반도체의 핵심 기술이 될 것이라고 이야기했습니다. 그 중에서도 칩 내 각종 전력 공급 장치들을 웨이퍼 뒷면에도 배치해 반도체 내 전력 관리를 '이원화'한다는 아이디어를 제시했습니다.

이 아이디어는 인텔이 최근 '파워 비아(Power Via)'라는 이름으로도 발표한 솔루션이기도 합니다. 복잡하게 엮여 있던 전력 공급 경로가 위아래로 나눠지면서, 전기 신호가 노이즈 없이 소자로 깔끔하게 전달될 수 있다는 장점이 있습니다.

GAA 트랜지스터를 넘은 3D 소자도 소개해 눈길을 끕니다. 연산을 담당하는 트랜지스터를 한 칩 안에 수직으로 쌓는 콘셉트죠. 평면에 트랜지스터를 배치하는 것보다 집적도를 극대화할 수 있는 방법입니다.

△이미지센서

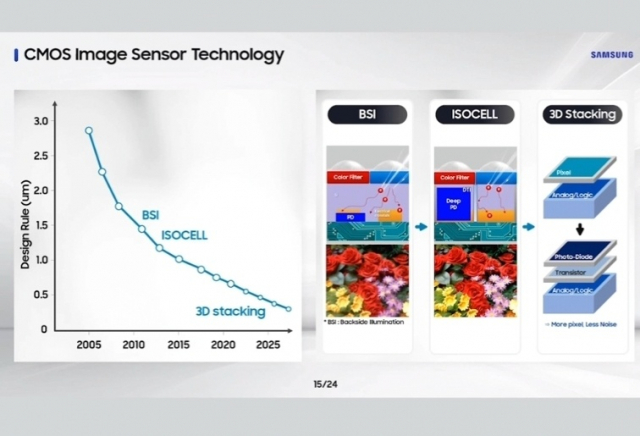

이미지 센서 업계에서는 현재까지 이미지를 확대하면 생기는 '깨짐' 현상을 최소화하기 위해 1억 화소(픽셀) 이상 제품이 개발된 상황이죠.

그러나 그만큼 화소 크기가 작아져 각 픽셀에 들어오는 빛 알갱이(광자·photon) 수가 기존보다 줄어들고, 픽셀 간 간섭이 심해지며 화질 저하가 발생하는 것이 문제입니다.

삼성전자는 픽셀 사이 칸막이(아이소셀·ISOCELL)를 쳐서 광자가 다른 픽셀로 넘어가 사고를 치지 않도록 방지하는 등 각고의 노력을 하며 이미지센서 기술을 발전시켰습니다.

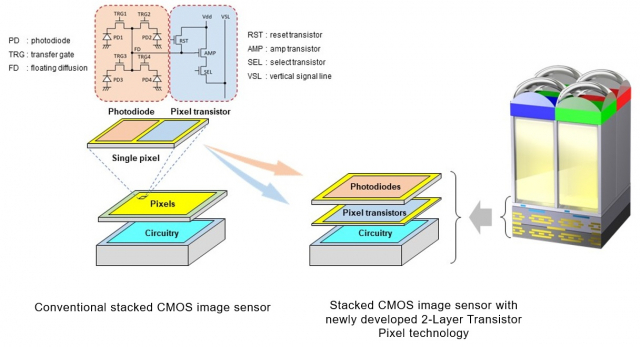

이번에 김 부사장이 새롭게 소개한 차세대 이미지센서 구조는 3D 스태킹 이미지센서입니다.

기존에는 ‘픽셀 영역’과 변환 장치 등 로직 반도체 영역만을 구분했지만, 이제 픽셀 안에 있는 구성 요소까지 구분해 3차원 적층한다는 콘셉트인데요.

조금 더 구체적으로 살펴보면, 픽셀 영역 내 렌즈와 컬러필터 뒤에 함께 붙어있는 포토다이오드와 트랜지스터를 분리해 개별 층으로 만든다는 이야기입니다.

포토다이오드는 렌즈를 통해 들어온 광자의 양과 세기를 파악해 전압을 만들어내는 그릇이고요. 트랜지스터는 이 그릇을 제어하고 생성된 전기 신호를 다른 곳으로 옮기는 역할인데요. 이 둘은 평면에 나란히 자리하고 있습니다. 하지만 둘을 평면이 아닌 수직으로 쌓는 방식을 택하면, 면적이 절반으로 줄어드는 셈이니 화소 수를 더 늘릴 수 있다는 얘기죠. 그림을 참고해 주세요.

이 기술은 지난해 12월 삼성전자의 이미지센서 라이벌 소니가 개발했다고 발표한 바 있습니다. 삼성전자는 과연 어떤 3D 스태킹 기술로 대응을 할지 관심이 모아집니다.

◇공정 변화

칩 구조 변화와 크기 감소를 위한 제조 공정 혁신도 발표에서 언급이 됐는데요. 반도체 공정의 핵심인 증착·식각 분야 위주로 미래 기술이 소개됐습니다.

△증착

증착은 반도체 공정 중 얇은 막(박막)을 쌓는 과정입니다. 한 개 칩을 만들기 위해 웨이퍼 위에 박막을 수백 번의쌓고, 깎아내는 반도체 공정 과정 중 막을 '쌓는' 과정에 해당하죠.

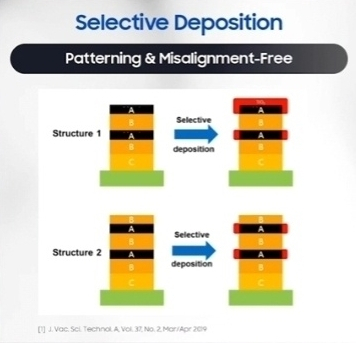

김 부사장이 이번에 언급한 차세대 증착 기술은 '선택적 증착(Selective Deposition)' 입니다. 쉽게 말하면 내가 원하는 곳에만 막을 씌운다는 것인데요.

기존 증착은 마치 도로 위에 눈이 쌓이는 것처럼 상대적으로 넓은 범위에 박막을 형성하지만, 선택적 증착은 특정 영역과 화학 소재 간 '케미'로 맞춤형 박막을 씌울 수 있는 것이죠.

또 이 방법은 박막의 면적 축소를 야기하면서 저항 값을 높게 만드는 일부 공정을 생략한다는 장점이 있습니다. 따라서 전류가 저항 없이 빠르게 흘러야 하는 ‘배선’을 만들 때 각광받는 기술입니다.

하지만 최근 칩 구석의 미세한 부분에 박막을 씌워야 할 경우가 생기고, 3D 소자 구조가 많아지면서 선택적 증착 쓰임새가 더욱 늘어나고 있습니다. 김 부사장은 "타겟 표면에만 원하는 막을 증착할 수 있어 3D '측면' 증착도 가능할 것으로 보인다"고 말했습니다.

△식각(ALE·극저온)

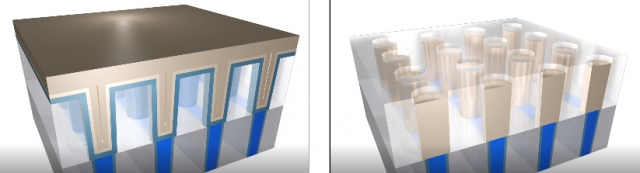

식각은 반도체 웨이퍼 위에 쌓은 막을 ‘깎아내는’ 공정인데요. 김형섭 부사장은 식각 분야에서의 미래 기술로 원자층식각(ALE) 방법을 꼽았습니다.

기존에는 분자 단위로 회로를 깎던 것을, 원자층 단위로 아주 미세하게 깎아내면서 회로를 만든다는 콘셉트입니다.

우리가 자주 가는 배스킨라빈스 31 아이스크림으로 비유해보면 이해가 수월합니다.

가게 직원 분이 맛있는 '엄마는 외계인' 아이스크림을 퍼주시는 상황을 가정해봅시다. 거대한 스쿱으로 퍼서 표면을 깎는 것이 일반적인 식각이라면, 티스푼으로 특정 구간을 깊게·표면을 고르는 작업까지 진행하면서·아주 천천히 세밀하게 퍼주시는 것이 바로 ALE 콘셉트입니다.

기존 식각에 비해 과정이 상당히 복잡하고 시간이 오래 걸린다는 문제를 극복해야 합니다.

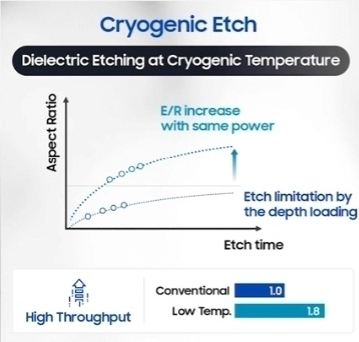

또다른 식각 방법으로 '극저온(Cryogenic)' 식각이 언급됐습니다.

식각 공정 중 웨이퍼 아래의 열을 기존보다 크게 낮춰서 공정을 진행하는 방법인데요. 전기가 통하지 않는 단단한 절연막을 식각해야 할 때, 이 방법을 쓰면 생산성을 높이면서 더 깊은 구멍을 빠르게 파낼 수 있다는 게 김 부사장 설명입니다. 균일성과 수율 문제를 극복하는 게 관건입니다.

이렇게 반도체 구조와 공정, 장비 및 소재를 혁신적으로 바꾸려면 생태계 간 협력이 필수입니다. 김형섭 부사장은 연설 말미에 "미래에는 더 많은 혁신이 필요할 것이고, 반도체 업계의 무한한 협력을 통해 가능할 것이라고 생각한다"고 밝혔습니다.

국내 반도체 생태계의 혁신 기술 협력이 더욱 활발하게 일어나길 바라면서 기사를 마무리하겠습니다. 감사합니다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com