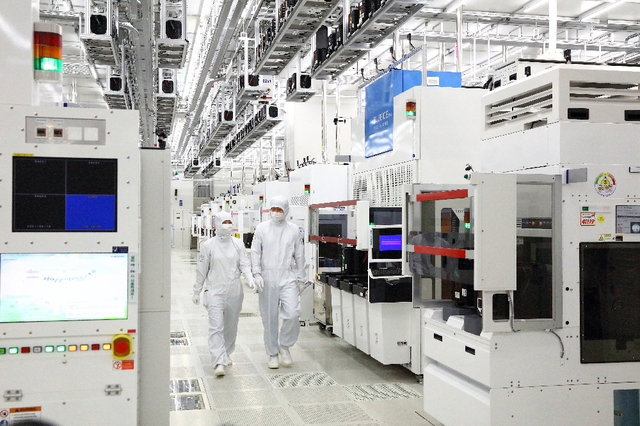

삼성전자(005930)가 파운드리(반도체 위탁생산) 4나노미터(㎚·10억 분의 1미터) 공정에서 업계 1위인 대만 TSMC와의 수율(완제품 중 양품 비율) 격차를 사실상 지웠다는 주장이 나왔다.

17일 정보기술(IT) 팁스터(정보유출자) ‘레베그너스(Revegnus)’는 애플의 경영진 미팅 회의록을 인용해 “4나노에서 삼성전자와 TSMC의 수율은 거의 같을 것으로 예상된다”고 밝혔다. 그러면서 “삼성전자가 예상보다 빠른 수율 회복을 기록하고 있다”고 언급했다.

레베그너스는 이와 함께 TSMC의 3나노 공정 수율에 대해 “최대 63% 수준”이라며 “가격인 4나노미터와 비교해 두 배가 됐다”고 덧붙였다.

업계에서는 실제로 삼성전자가 4나노 공정에서 괄목할 수준의 수율 개선을 이뤘다고 평가하고 있다. TSMC의 수율은 4나노에서 80% 안팎으로 예측된다. 이번 팁스터 주장이 아니라도 업계에서는 삼성전자가 기존 60% 수준으로 예측되던 4나노 수율을 70% 이상으로 끌어올렸을 것으로 예상하고 있다. 이와 관련해 삼성전자는 사업보고서에서 “4나노 2·3세대의 안정적인 수율을 확보했다”며 “2023년 상반기 양산을 준비 중”이라고 밝히기도 했다.

삼성전자의 4나노 공정은 핀펫(FinFET) 기반 SF4E(4LPE)로 시작해 SF4(4LPP)를 거쳐 현재 3세대인 SF4P(4LPP+) 버전까지 나온 상태다. 초창기 버전인 SF4E에서는 낮은 수율로 고전했지만 올해 SF4P 버전에서 급격한 개선이 이뤄진 것으로 알려졌다. 삼성전자는 4나노 3세대 공정으로 구글의 스마트폰 픽셀8의 ‘텐서3’ 칩을 위탁 생산하는 것으로 전해졌다. 업계에서는 올해 하반기 제품 출시 이후 삼성전자의 구체적인 ‘파운드리 성적표’를 가늠해 볼 수 있을 것으로 예상하고 있다.

삼성전자는 4나노에서 TSMC와의 기술·생산 격차를 근접한 수준까지 추격한 뒤 3나노에서 선두 경쟁에 나서겠다는 전략이다. 삼성전자는 3나노에서 세계 최초로 차세대 트랜지스터 구조인 게이트올어라운드(GAA) 기술을 적용해 초도 양산에 성공했다. GAA는 기존 핀펫 구조와 비교해 공정 미세화에 따른 트랜지스터의 성능 저하를 극복하고 데이터 처리 속도·전력 효율을 높일 수 있어 차세대 반도체 핵심 기술로 꼽힌다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

jin@sedaily.com

jin@sedaily.com